Daniel Avella Ordonez

Computer Systems Engineer

© 2026 All rights reserved.

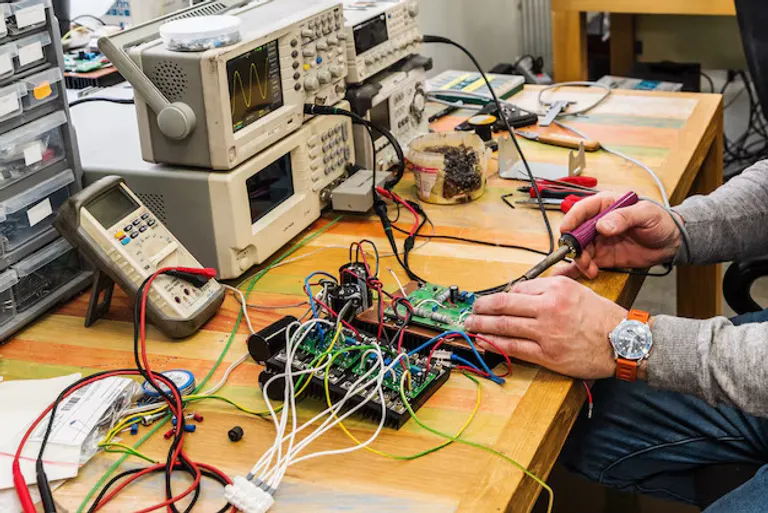

Multistage BJT Amplifier Design & Validation

Description

Toronto Metropolitan University

March 2025

Designed and validated a multistage BJT amplifier using single-supply biasing, small-signal modeling, and gain/bandwidth optimization. Verified performance through Multisim simulations, parametric sweeps, and corner analysis.